如果您无法下载资料,请参考说明:

1、部分资料下载需要金币,请确保您的账户上有足够的金币

2、已购买过的文档,再次下载不重复扣费

3、资料包下载后请先用软件解压,在使用对应软件打开

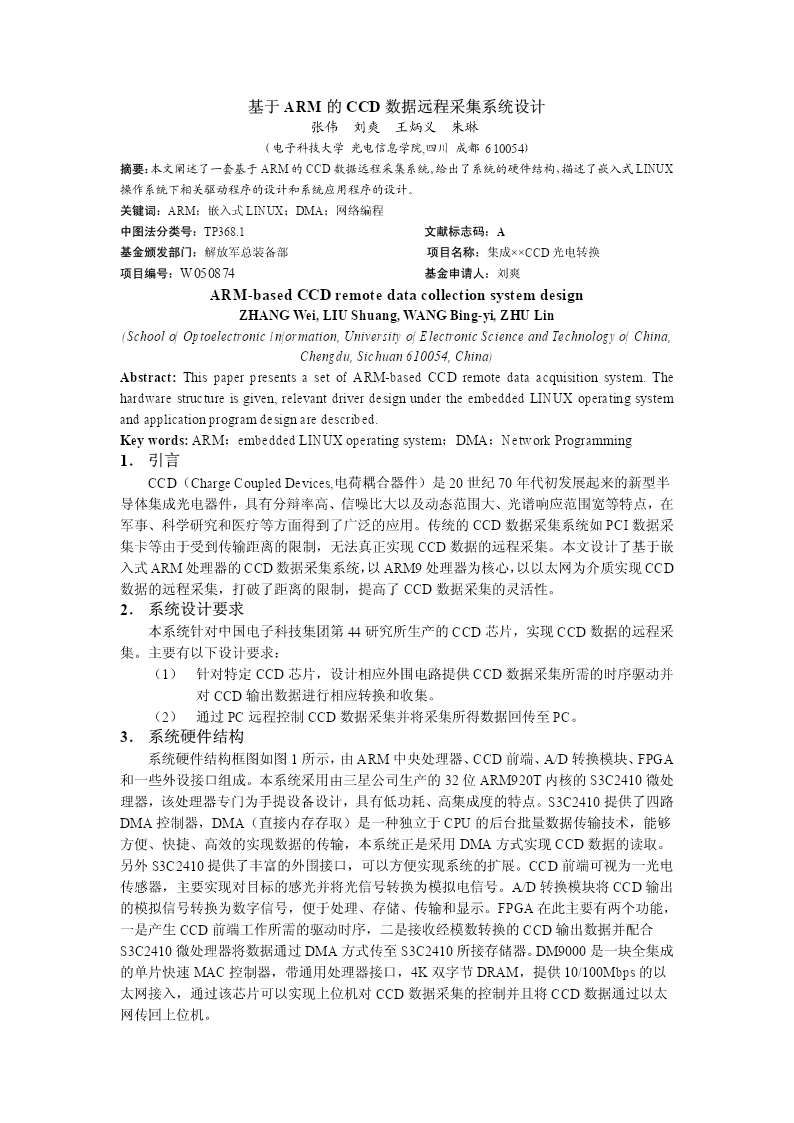

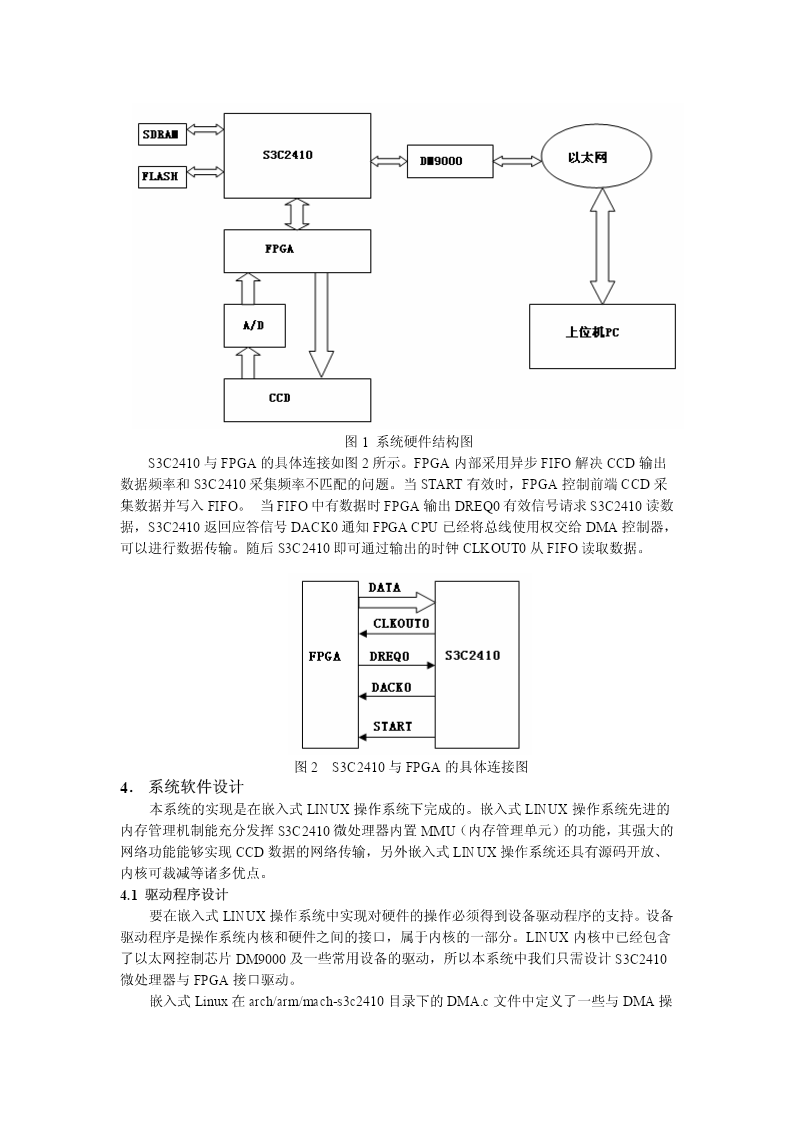

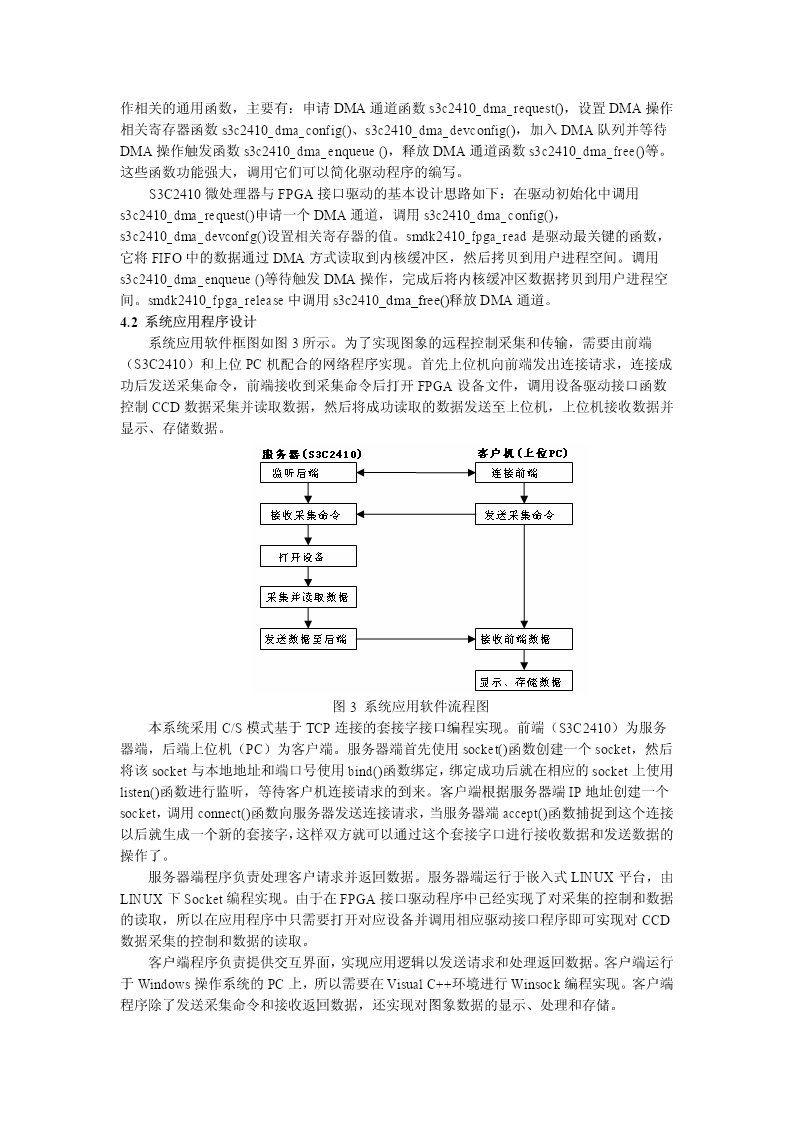

基于ARM的CCD数据远程采集系统设计 张伟刘爽王炳义朱琳 (电子科技大学光电信息学院,四川成都610054) 摘要:本文阐述了一套基于ARM的CCD数据远程采集系统。给出了系统的硬件结构,描述了嵌入式LINUX 操作系统下相关驱动程序的设计和系统应用程序的设计。 关键词:ARM;嵌入式LINUX;DMA;网络编程 中图法分类号:TP368.1文献标志码:A 基金颁发部门:解放军总装备部项目名称:集成××CCD光电转换 项目编号:W050874基金申请人:刘爽 ARM-basedCCDremotedatacollectionsystemdesign ZHANGWei,LIUShuang,WANGBing-yi,ZHULin (SchoolofOptoelectronicInformation,UniversityofElectronicScienceandTechnologyofChina, Chengdu,Sichuan610054,China) Abstract:ThispaperpresentsasetofARM-basedCCDremotedataacquisitionsystem.The hardwarestructureisgiven,relevantdriverdesignundertheembeddedLINUXoperatingsystem andapplicationprogramdesignaredescribed. Keywords:ARM;embeddedLINUXoperatingsystem;DMA;NetworkProgramming 1.引言 CCD(ChargeCoupledDevices,电荷耦合器件)是20世纪70年代初发展起来的新型半 导体集成光电器件,具有分辩率高、信噪比大以及动态范围大、光谱响应范围宽等特点,在 军事、科学研究和医疗等方面得到了广泛的应用。传统的CCD数据采集系统如PCI数据采 集卡等由于受到传输距离的限制,无法真正实现CCD数据的远程采集。本文设计了基于嵌 入式ARM处理器的CCD数据采集系统,以ARM9处理器为核心,以以太网为介质实现CCD 数据的远程采集,打破了距离的限制,提高了CCD数据采集的灵活性。 2.系统设计要求 本系统针对中国电子科技集团第44研究所生产的CCD芯片,实现CCD数据的远程采 集。主要有以下设计要求: (1)针对特定CCD芯片,设计相应外围电路提供CCD数据采集所需的时序驱动并 对CCD输出数据进行相应转换和收集。 (2)通过PC远程控制CCD数据采集并将采集所得数据回传至PC。 3.系统硬件结构 系统硬件结构框图如图1所示,由ARM中央处理器、CCD前端、A/D转换模块、FPGA 和一些外设接口组成。本系统采用由三星公司生产的32位ARM920T内核的S3C2410微处 理器,该处理器专门为手提设备设计,具有低功耗、高集成度的特点。S3C2410提供了四路 DMA控制器,DMA(直接内存存取)是一种独立于CPU的后台批量数据传输技术,能够 方便、快捷、高效的实现数据的传输,本系统正是采用DMA方式实现CCD数据的读取。 另外S3C2410提供了丰富的外围接口,可以方便实现系统的扩展。CCD前端可视为一光电 传感器,主要实现对目标的感光并将光信号转换为模拟电信号。A/D转换模块将CCD输出 的模拟信号转换为数字信号,便于处理、存储、传输和显示。FPGA在此主要有两个功能, 一是产生CCD前端工作所需的驱动时序,二是接收经模数转换的CCD输出数据并配合 S3C2410微处理器将数据通过DMA方式传至S3C2410所接存储器。DM9000是一块全集成 的单片快速MAC控制器,带通用处理器接口,4K双字节DRAM,提供10/100Mbps的以 太网接入,通过该芯片可以实现上位机对CCD数据采集的控制并且将CCD数据通过以太 网传回上位机。 图1系统硬件结构图 S3C2410与FPGA的具体连接如图2所示。FPGA内部采用异步FIFO解决CCD输出 数据频率和S3C2410采集频率不匹配的问题。当START有效时,FPGA控制前端CCD采 集数据并写入FIFO。当FIFO中有数据时FPGA输出DREQ0有效信号请求S3C2410读数 据,S3C2410返回应答信号DACK0通知FPGACPU已经将总线使用权交给DMA控制器, 可以进行数据传输。随后S3C2410即可通过输出的时钟CLKOUT0从FIFO读取数据。 图2S3C2410与FPGA的具体连接图 4.系统软件设计 本系统的实现是在嵌入式LINUX操作系统下完成的。嵌入式LINUX操作系统先进的 内存管理机制能充分发挥S3C2410微处理器内置MMU(内存管理单元)的功能,其强大的

qw****27

实名认证

实名认证

内容提供者

内容提供者

最近下载