如果您无法下载资料,请参考说明:

1、部分资料下载需要金币,请确保您的账户上有足够的金币

2、已购买过的文档,再次下载不重复扣费

3、资料包下载后请先用软件解压,在使用对应软件打开

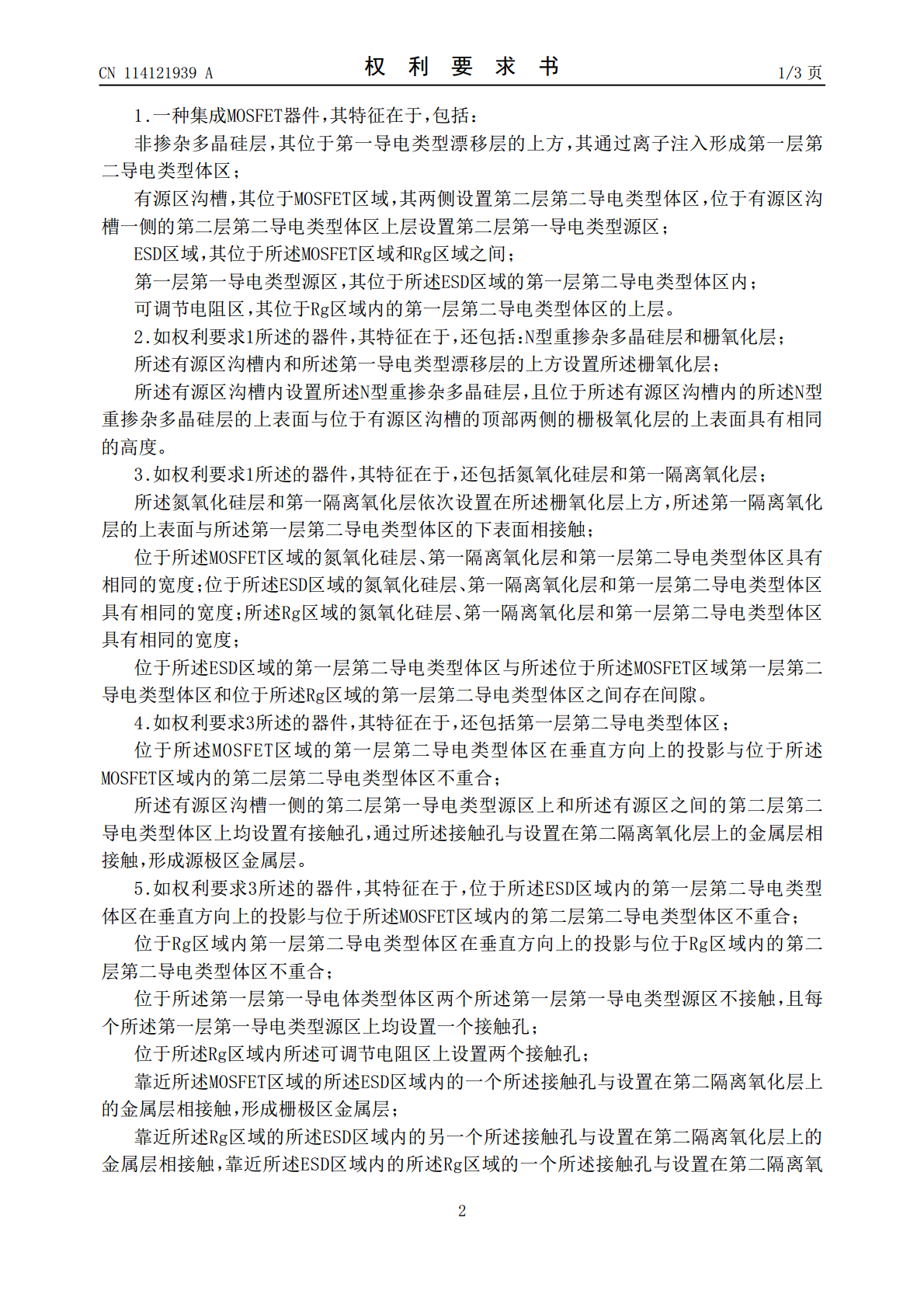

(19)中华人民共和国国家知识产权局(12)发明专利申请(10)申请公布号CN114121939A(43)申请公布日2022.03.01(21)申请号202111408815.X(22)申请日2021.11.24(71)申请人华羿微电子股份有限公司地址710018陕西省西安市未央区经济技术开发区草滩生态产业园尚稷路8928号(72)发明人完颜文娟袁力鹏苏毅常虹(74)专利代理机构广州三环专利商标代理有限公司44202代理人党娟娟郭永丽(51)Int.Cl.H01L27/02(2006.01)H01L21/336(2006.01)H01L29/78(2006.01)权利要求书3页说明书10页附图8页(54)发明名称一种集成MOSFET器件及制备方法(57)摘要本发明公开了一种集成MOSFET器件及制备方法,涉及半导体功率器件领域。通过ESD多晶硅层作为掩膜版阻挡P型体区在外围的注入达到器件耐压的目的,且在Rg区域内形成可调节电阻区,可完善器件的功能。包括:非掺杂多晶硅层,其位于第一导电类型漂移层的上方,其通过离子注入形成第一层第二导电类型体区;有源区沟槽,其位于MOSFET区域,其两侧设置第二层第二导电类型体区,位于有源区沟槽一侧的第二层第二导电类型体区上层设置第二层第一导电类型源区;ESD区域,其位于所述MOSFET区域和Rg区域之间;第一层第一导电类型源区,其位于所述ESD区域的第一层第二导电类型体区内;可调节电阻区,其位于Rg区域内的第一层第二导电类型体区的上层。CN114121939ACN114121939A权利要求书1/3页1.一种集成MOSFET器件,其特征在于,包括:非掺杂多晶硅层,其位于第一导电类型漂移层的上方,其通过离子注入形成第一层第二导电类型体区;有源区沟槽,其位于MOSFET区域,其两侧设置第二层第二导电类型体区,位于有源区沟槽一侧的第二层第二导电类型体区上层设置第二层第一导电类型源区;ESD区域,其位于所述MOSFET区域和Rg区域之间;第一层第一导电类型源区,其位于所述ESD区域的第一层第二导电类型体区内;可调节电阻区,其位于Rg区域内的第一层第二导电类型体区的上层。2.如权利要求1所述的器件,其特征在于,还包括:N型重掺杂多晶硅层和栅氧化层;所述有源区沟槽内和所述第一导电类型漂移层的上方设置所述栅氧化层;所述有源区沟槽内设置所述N型重掺杂多晶硅层,且位于所述有源区沟槽内的所述N型重掺杂多晶硅层的上表面与位于有源区沟槽的顶部两侧的栅极氧化层的上表面具有相同的高度。3.如权利要求1所述的器件,其特征在于,还包括氮氧化硅层和第一隔离氧化层;所述氮氧化硅层和第一隔离氧化层依次设置在所述栅氧化层上方,所述第一隔离氧化层的上表面与所述第一层第二导电类型体区的下表面相接触;位于所述MOSFET区域的氮氧化硅层、第一隔离氧化层和第一层第二导电类型体区具有相同的宽度;位于所述ESD区域的氮氧化硅层、第一隔离氧化层和第一层第二导电类型体区具有相同的宽度;所述Rg区域的氮氧化硅层、第一隔离氧化层和第一层第二导电类型体区具有相同的宽度;位于所述ESD区域的第一层第二导电类型体区与所述位于所述MOSFET区域第一层第二导电类型体区和位于所述Rg区域的第一层第二导电类型体区之间存在间隙。4.如权利要求3所述的器件,其特征在于,还包括第一层第二导电类型体区;位于所述MOSFET区域的第一层第二导电类型体区在垂直方向上的投影与位于所述MOSFET区域内的第二层第二导电类型体区不重合;所述有源区沟槽一侧的第二层第一导电类型源区上和所述有源区之间的第二层第二导电类型体区上均设置有接触孔,通过所述接触孔与设置在第二隔离氧化层上的金属层相接触,形成源极区金属层。5.如权利要求3所述的器件,其特征在于,位于所述ESD区域内的第一层第二导电类型体区在垂直方向上的投影与位于所述MOSFET区域内的第二层第二导电类型体区不重合;位于Rg区域内第一层第二导电类型体区在垂直方向上的投影与位于Rg区域内的第二层第二导电类型体区不重合;位于所述第一层第一导电体类型体区两个所述第一层第一导电类型源区不接触,且每个所述第一层第一导电类型源区上均设置一个接触孔;位于所述Rg区域内所述可调节电阻区上设置两个接触孔;靠近所述MOSFET区域的所述ESD区域内的一个所述接触孔与设置在第二隔离氧化层上的金属层相接触,形成栅极区金属层;靠近所述Rg区域的所述ESD区域内的另一个所述接触孔与设置在第二隔离氧化层上的金属层相接触,靠近所述ESD区域内的所述Rg区域的一个所述接触孔与设置在第二隔离氧2CN114121939A权利要求书2/3页化层上的金属层相接触,形成Rg区‑‑ESD区连接金属层;位于所述Rg区域的另一个所述接触孔与设置在第二隔离氧化层上的金属层相接触,形成栅

是笛****加盟

实名认证

实名认证

内容提供者

内容提供者

最近下载