如果您无法下载资料,请参考说明:

1、部分资料下载需要金币,请确保您的账户上有足够的金币

2、已购买过的文档,再次下载不重复扣费

3、资料包下载后请先用软件解压,在使用对应软件打开

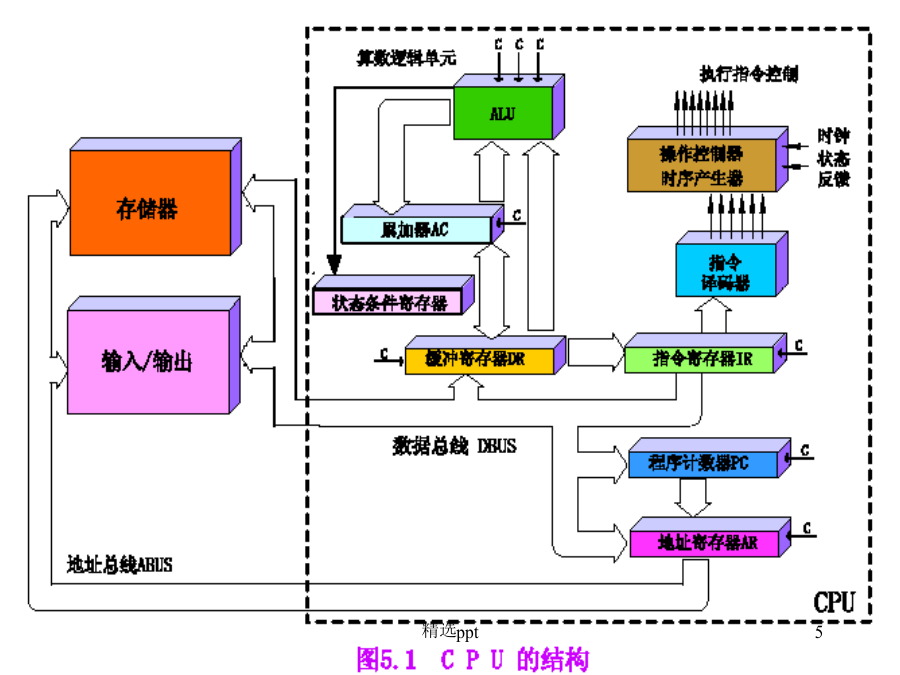

第五章中央处理器5.1CPU的组成和功能5.1.1CPU的功能★指令控制程序的顺序控制称为指令控制。由于程序是一个指令序列,这些指令的相互顺序不能任意颠倒,必须严格按程序规定的顺序进行。 ★操作控制一条指令的功能往往是由若干个操作信号的组合来实现的,因此,CPU管理并产生由内存取出的每条指令的操作信号,把各种操作信号送往相应的部件,从而控制这些部件按指令的要求进行动作。 ★时间控制对各种操作实施时间上的定时称为时间控制。在计算机中,各种指令的操作信号以及一条指令的整个执行过程都受到时间的严格定时。 ★数据加工数据加工就是对数据进行算术运算和逻辑运算处理。5.1.2CPU的基本组成5控制器 由程序计数器、指令寄存器、指令译码器、时序产生器和操作控制器组成,它是发布命令的“决策机构”,即完成协调和指挥整个计算机系统的操作。它的主要功能有: (1)从内存中取出一条指令,并指出下一条指令在内存中的位置; (2)对指令进行译码或测试,并产生相应的操作控制信号,以便启动规定的动作; (3)指挥并控制CPU、内存和输入/输出设备之间数据流动的方向。运算器 由算术逻辑单元(ALU)、累加寄存器、数据缓冲寄存器和状态条件寄存器组成,它是数据加工处理部件。相对控制器而言,运算器接受控制器的命令而进行动作,即运算器所进行的全部操作都是由控制器发出的控制信号来指挥的,所以它是执行部件。运算器有两个主要功能: (1)执行所有的算术运算; (2)执行所有的逻辑运算,并进行逻辑测试, 如零值测试或两个值的比较。5.1.3CPU中的主要寄存器1.数据缓冲寄存器(DR) 数据缓冲寄存器用来暂时存放由内存储器读出的一条指令或一个数据字;反之,当向内存存入一条指令或一个数据字时,也暂时将它们存放在数据缓冲寄存器中。 缓冲寄存器的作用是: (1)作为CPU和内存、外部设备之间信息传送的中转站; (2)补偿CPU和内存、外围设备之间在操作速度上的差别; (3)在单累加器结构的运算器中,数据缓冲寄存器还可兼作为操作数寄存器。2.指令寄存器(IR) 指令寄存器用来保存当前正在执行的一条指令。当执行一条指令时,先把它从内存取到缓冲寄存器中,然后再传送至指令寄存器。指令划分为操作码和地址码字段,由二进制数字组成。为了执行任何给定的指令,必须对操作码进行测试,以便识别所要求的操作。指令译码器就是做这项工作的。指令寄存器中操作码字段的输出就是指令译码器的输入。操作码一经译码后,即可向操作控制器发出具体操作的特定信号。3.程序计数器(PC) 为了保证程序能连续地执行下去,CPU必须具有某些手段来确定下一条指令的地址。而程序计数器正是起到这种作用,所以通常又称为指令计数器。在程序开始执行前必须将它的起始地址,即程序的一条指令所在的内存单元地址送入PC,因此PC的内容即是从内存提取的第一条指令的地址。当执行指令时,CPU将自动修改PC的内容,以便使其保持的总是将要执行的下一条指令的地址。由于大多数指令都是按顺序来执行的,所以修改的过程通常只是简单的对PC加1。 但是当遇到转移指令如JMP指令时,那么后继指令的地址(即PC的内容)必须从指令的地址段取得。在这种情况下下一条从内存取出的指令将由转移指令来规定,而不是像通常一样按顺序来取得。因此程序计数器的结构应当是具有寄存信息和计数两种功能的结构。4.地址寄存器(AR) 地址寄存器用来保存当前CPU所访问的内存单元的地址。由于在内存和CPU之间存在着操作速度上的差别,所以必须使用地址寄存器来保持地址信息,直到内存的读/写操作完成为止。 当CPU和内存进行信息交换,即CPU向内存存/取数据时,或者CPU从内存中读出指令时,都要使用地址寄存器和数据缓冲寄存器。同样,如果我们把外围设备的设备地址作为像内存的地址单元那样来看待,那么,当CPU和外围设备交换信息时,我们同样使用地址寄存器和数据缓冲寄存器。 地址寄存器的结构和数据缓冲寄存器、指令寄存器一样,通常使用单纯的寄存器结构。信息的存入一般采用电位-脉冲方式,即电位输入端对应数据信息位,脉冲输入端对应控制信号,在控制信号作用下,瞬时地将信息打入寄存器。5.累加寄存器(AC) 累加寄存器AC通常简称为累加器,它是一个通用寄存器。其功能是:当运算器的算术逻辑单元ALU)执行算术或逻辑运算时,为ALU提供一个工作区。累加寄存器暂时存放ALU运算的结果信息。显然,运算器中至少要有一个累加寄存器。 目前CPU中的累加寄存器,多达16个,32个,甚至更多。当使用多个累加器时,就变成通用寄存器堆结构,其中任何一个可存放源操作数,也可存放结果操作数。在这种情况下,需要在指令格式中对寄存器号加以编址。6.状态条件寄存器(PSW) 状态条件寄存器保存由算术指令和逻辑指令运行或测试的结果建立的各种条

涵蓄****09

实名认证

实名认证

内容提供者

内容提供者

最近下载

最新上传

浙江省宁波市2024-2025学年高三下学期4月高考模拟考试语文试题及参考答案.docx

汤成难《漂浮于万有引力中的房屋》阅读答案.docx

四川省达州市普通高中2025届第二次诊断性检测语文试卷及参考答案.docx

山西省吕梁市2025年高三下学期第二次模拟考试语文试题及参考答案.docx

山西省部分学校2024-2025学年高二下学期3月月考语文试题及参考答案.docx

山西省2025年届高考考前适应性测试(冲刺卷)语文试卷及参考答案.docx

全国各地市语文中考真题名著阅读分类汇编.docx

七年级历史下册易混易错84条.docx

湖北省2024-2025学年高一下学期4月期中联考语文试题及参考答案.docx

黑龙江省大庆市2025届高三第三次教学质量检测语文试卷及参考答案.docx