如果您无法下载资料,请参考说明:

1、部分资料下载需要金币,请确保您的账户上有足够的金币

2、已购买过的文档,再次下载不重复扣费

3、资料包下载后请先用软件解压,在使用对应软件打开

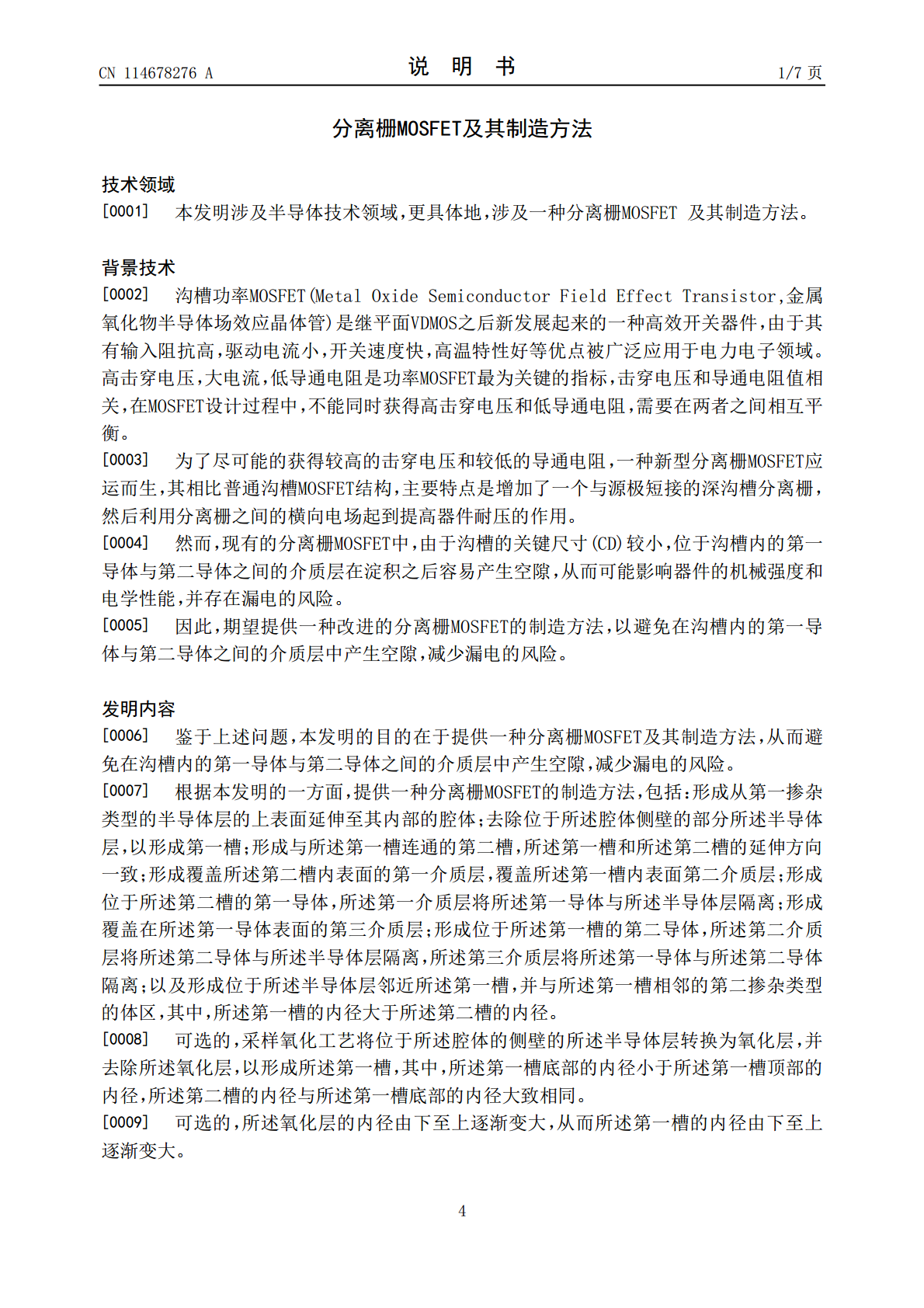

(19)国家知识产权局(12)发明专利申请(10)申请公布号CN114678276A(43)申请公布日2022.06.28(21)申请号202111635879.3(22)申请日2021.12.29(71)申请人杭州芯迈半导体技术有限公司地址310051浙江省杭州市滨江区西兴街道联慧街6号(72)发明人蔡金勇董仕达王加坤(74)专利代理机构北京成创同维知识产权代理有限公司11449专利代理师蔡纯杨思雨(51)Int.Cl.H01L21/336(2006.01)H01L29/78(2006.01)H01L29/423(2006.01)权利要求书2页说明书7页附图11页(54)发明名称分离栅MOSFET及其制造方法(57)摘要本申请公开了一种分离栅MOSFET及其制造方法。该制造方法包括:形成从第一掺杂类型的半导体层的上表面延伸至其内部的腔体;去除位于腔体侧壁的部分半导体层,以形成第一槽;形成与第一槽连通的第二槽,第一槽和第二槽的延伸方向一致;形成覆盖第二槽内表面的第一介质层,覆盖第一槽内表面第二介质层;形成位于第二槽的第一导体,第一介质层将第一导体与半导体层隔离;形成覆盖在第一导体表面的第三介质层;形成位于第一槽的第二导体,第二介质层将第二导体与半导体层隔离,第三介质层将第一导体与第二导体隔离;形成位于半导体层邻近第一槽,并与第一槽相邻的第二掺杂类型的体区,第一槽的内径大于第二槽的内径。该制造方法扩展了工艺窗口。CN114678276ACN114678276A权利要求书1/2页1.一种分离栅MOSFET的制造方法,其特征在于,包括:形成从第一掺杂类型的半导体层的上表面延伸至其内部的腔体;去除位于所述腔体侧壁的部分所述半导体层,以形成第一槽;形成与所述第一槽连通的第二槽,所述第一槽和所述第二槽的延伸方向一致;形成覆盖所述第二槽内表面的第一介质层,覆盖所述第一槽内表面第二介质层;形成位于所述第二槽的第一导体,所述第一介质层将所述第一导体与所述半导体层隔离;形成覆盖在所述第一导体表面的第三介质层;形成位于所述第一槽的第二导体,所述第二介质层将所述第二导体与所述半导体层隔离,所述第三介质层将所述第一导体与所述第二导体隔离;以及形成位于所述半导体层邻近所述第一槽,并与所述第一槽相邻的第二掺杂类型的体区,其中,所述第一槽的内径大于所述第二槽的内径。2.根据权利要求1所述的制造方法,其特征在于,采样氧化工艺将位于所述腔体的侧壁的所述半导体层转换为氧化层,并去除所述氧化层,以形成所述第一槽,其中,所述第一槽底部的内径小于所述第一槽顶部的内径,所述第二槽的内径与所述第一槽底部的内径大致相同。3.根据权利要求2所述的制造方法,其特征在于,所述氧化层的内径由下至上逐渐变大,从而所述第一槽的内径由下至上逐渐变大。4.根据权利要求2或3所述的制造方法,其特征在于,通过调节所述氧化工艺中的氧化剂的浓度,控制去除所述腔体的侧壁的厚度。5.根据权利要求1所述的制造方法,其特征在于,所述第一介质层的厚度大于所述第二介质层的厚度。6.根据权利要求1所述的制造方法,其特征在于,还包括:形成位于所述体区中的源区,所述源区为所述第一掺杂类型;形成位于所述源区上方的层间介质层;以及形成位于所述层间介质层上方的源极电极。7.根据权利要求1所述的制造方法,其特征在于,还包括:形成位于所述体区中的第二掺杂类型的体接触区;以及形成穿透所述层间介质层以及源区到达所述体接触区的导电通道,所述源极电极经由所述导电通道连接至所述体接触区。8.根据权利要求1所述的制造方法,其特征在于,所述半导体层形成于半导体衬底之上,所述半导体衬底位于所述半导体层的下表面,所述半导体层的上表面与所述下表面相对,所述制造方法还包括:形成位于所述半导体衬底的下表面的漏极电极。9.一种分离栅MOSFET,其特征在于,包括:第一掺杂类型的半导体层;从所述半导体层的上表面延伸至其内部的第一槽、与所述第一槽的底部连通的第二槽,所述第一槽和所述第二槽延伸方向一致;2CN114678276A权利要求书2/2页覆盖所述第二槽内表面的第一介质层,覆盖所述第一槽内表面第二介质层,以及位于所述第一介质层与第二介质层之间的第三介质层;位于所述第二槽的第一导体和位于所述第一槽的第二导体,其中,所述第一介质层将所述第一导体与所述半导体层隔离,所述第二介质层将所述第二导体与所述半导体层隔离,所述第三介质层将所述第一导体与所述第二导体隔离;以及位于所述半导体层邻近所述第一槽,并与所述第一槽相邻的第二掺杂类型的体区,其中,所述第一槽是通过去除位于腔体侧壁的部分所述半导体层形成的,所述第一槽的内径大于所述第二槽的内径。10.根据权利要求9所述的分离栅MOSFET,其特征在于,所述第一槽的内径由下至上逐渐变大。11.根据权利要求9所述的分离栅M

努力****凌芹

实名认证

实名认证

内容提供者

内容提供者

最近下载