如果您无法下载资料,请参考说明:

1、部分资料下载需要金币,请确保您的账户上有足够的金币

2、已购买过的文档,再次下载不重复扣费

3、资料包下载后请先用软件解压,在使用对应软件打开

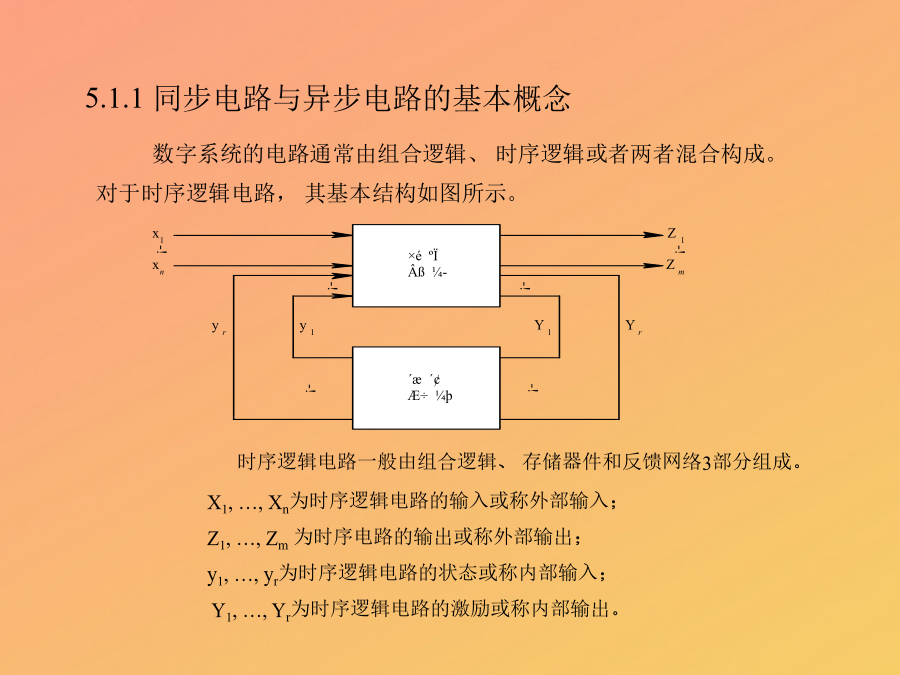

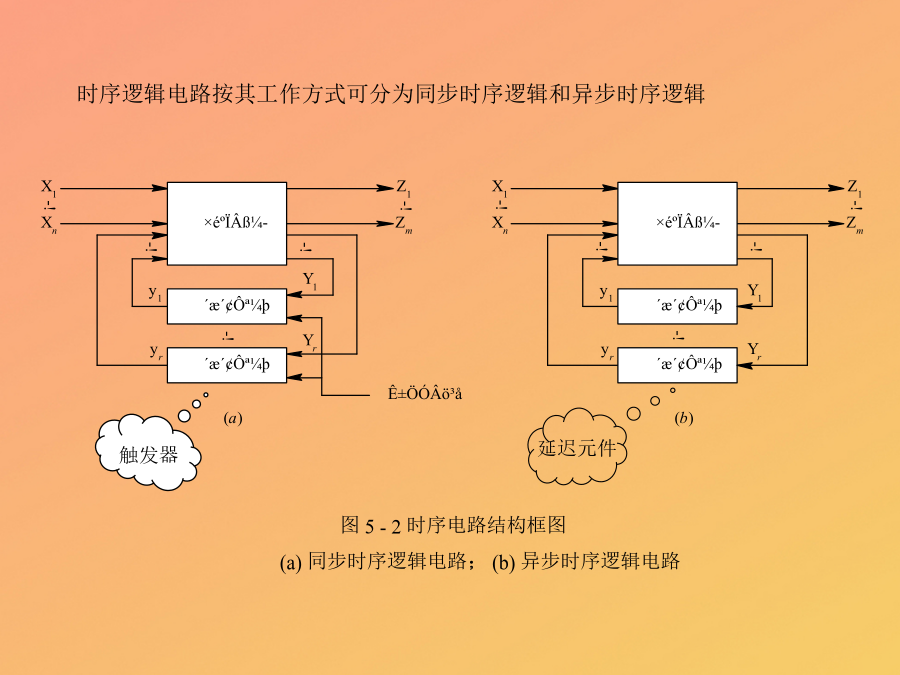

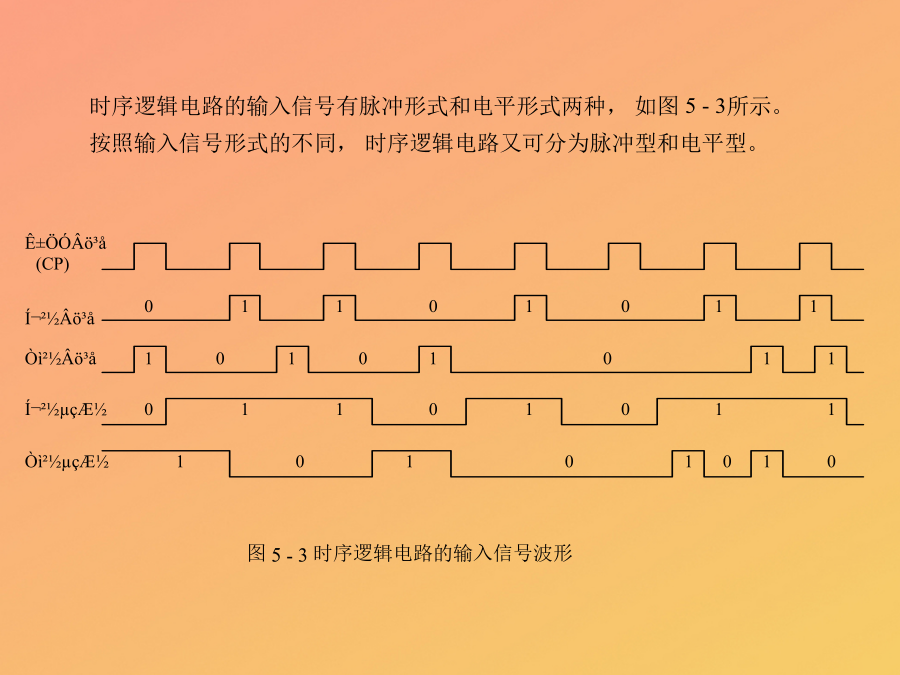

第5章现场可编程逻辑系统的设计技巧5.1同步电路设计技巧5.1.1同步电路与异步电路的基本概念 数字系统的电路通常由组合逻辑、时序逻辑或者两者混合构成。对于时序逻辑电路,其基本结构如图所示。 图5-2时序电路结构框图 (a)同步时序逻辑电路;(b)异步时序逻辑电路将图5-23所示电路改为流水线的结构,如图5-24所示,即在两级串行组合逻辑之间嵌入触发器PIPE-FFS。 图5-11异步“清除”电路 对于如图所示的时钟分配电路,为了减少时钟CLK1和CLK2之间的时钟偏移,可采用额外的缓冲器BUFG来降低CLK2的时钟偏移。 1FPGA实现中的基本时延 图5-16异步输入信号同步化电路 这时需要分两种情况考虑: 图5-6不好的时钟分配电路 对于如图5-17所示电路,前后两个触发器之间为某一逻辑功能,CLK1和CLK2分别是前后两个触发器的时钟信号。 图5-18附加触发器以防止出现不确定态 1. 但是,这样的电路并不能完全抑制时钟波形的变形。 但是,这样的电路并不能完全抑制时钟波形的变形。 也可以反过来,采用预期的时钟频率来决定电路设计中允许使用的CLB的串级数。 在同步逻辑电路的系统中,如果存在两个时钟信号,且对于包容于CLK1和CLK2之间的信号,需要和CLK2信号同步。 (a)不好的设计; 当CLK2-CE信号是高扇出时,可省略BUFG缓冲器。 (b)电路波形示意 但是,直接用门控时钟来控制电路的状态变化,由于各种原因造成的时钟信号的毛刺将直接影响电路的正常工作。5.1.2FPGA现场集成中常见的问题 在采用FPGA这样已规范的可编程逻辑阵列和可编程连线的有限资源,去实现不同功能的时序逻辑电路系统时,如何把握随机的布局、布线带来的时延对系统逻辑的影响,如何避免局部逻辑资源时延特征和不同的时序电路形式的制约,如何有效利用FPGA的特征逻辑结构去优化电路设计,都是一个设计工程师在设计中必须考虑的问题。 在采用FPGA的数字时序逻辑的现场集成,特别是对于同步电路的设计实现中,我们常遇到的主要问题有以下几种。 图5-4时钟使能信号电路图5-5在电路中加入CE信号的形式 (a)增添具有CE脚的触发器;(b)附加逻辑控制端CE图5-6不好的时钟分配电路图5-8门控时钟的毛刺产生原理图5-9避免时钟毛刺的电路图5-11异步“清除”电路图5-13避免Set/Reset信号中毛刺的影响的分析 (a)不好的设计;(b)好的设计4.在同步电路设计中,时钟偏移及不确定信号电平的影响 时序电路在FPGA中实现时,由于各部分连线长短不一致,导致其虽然多个触发器共用一个时钟信号,但触发器时钟端的信号延时并不相同,信号会发生不同的畸变,构成时钟信号偏移。 如图5-14所示,图5-14(a)中标出时钟信号的不同时延,对照图5-14(c)的信号波形,可以分析,由于时钟信号到达触发器的端口处的信号发生畸变和不同的时延,该移位寄存器将不能正常工作。 图5-14同步电路中时钟偏移的影响图5-15时钟信号建立与保持时间的影响图5-16异步输入信号同步化电路图5-17双CLK的电路图5-18附加触发器以防止出现不确定态 (a)电路图;(b)电路波形示意图5-19电路原理和波形示意5.2多级逻辑的设计技巧图5-20多级CLB的时延模型5.2.2流水线的基本概念 为了提高多级逻辑的系统速度,引入“流水线”的概念。 流水线设计:把在一个时钟周期内执行的逻辑操作分成几步较小的操作,并在多个较高速的时钟内完成。 图5-22的数据通路中的逻辑被分为3小部分。如果它的tPD为x,则该电路的最高时钟频率为1/x。而在图5-22(b)中,假设在理想情况下每部分的tPD为x/3,则它的时钟频率可提高到原来的3倍。当然,我们在计算中并没有包括电路中寄存器的时钟——输出时延和信号建立时间,因此实际的延迟应比x/3稍大。在忽略它们的情况下,我们可以看到,流水线技术可以用来提高系统的数据流量,也就是在单位时间内所处理的数据量。但是,采用这种方法的代价是输出信号将相对于输入滞后3个时钟周期。因此必须根据这种情况对设计进行修改。这时需要分两种情况考虑: (b)附加逻辑控制端CE 图5-11异步“清除”电路 但是,这样的电路并不能完全抑制时钟波形的变形。 ·CLK1快于CLK2(CLK1的脉宽小于CLK2)。 也可以有意识地对与门输入端引入一个CLB时延,如图5-10所示,同样可以将门控时钟毛刺形成的可能性降低。 采用流水线技术,是实现多级逻辑的系统时钟提升的有效途径。 图5-2时序电路结构框图 图5-3时序逻辑电路的输入信号波形 图5-2时序电路结构框图 图5-16所示为异步输入信号同步化的电路举例。 图5-12“清除”信号的同步化解决方案 所以实际上往往没有必要在CPLD中应用流水线技术。 图5-

王子****青蛙

实名认证

实名认证

内容提供者

内容提供者

最近下载