如果您无法下载资料,请参考说明:

1、部分资料下载需要金币,请确保您的账户上有足够的金币

2、已购买过的文档,再次下载不重复扣费

3、资料包下载后请先用软件解压,在使用对应软件打开

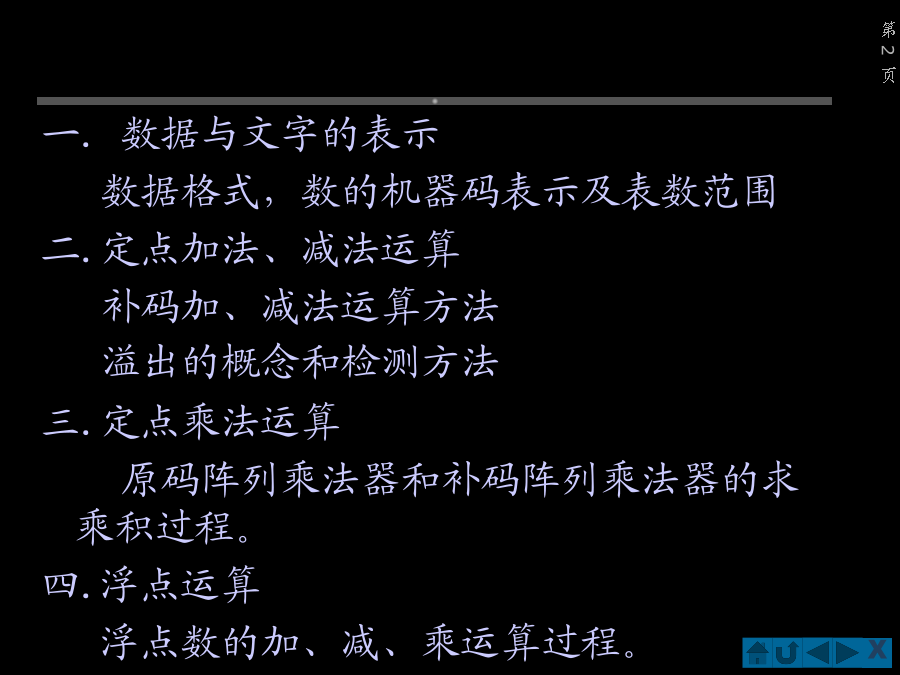

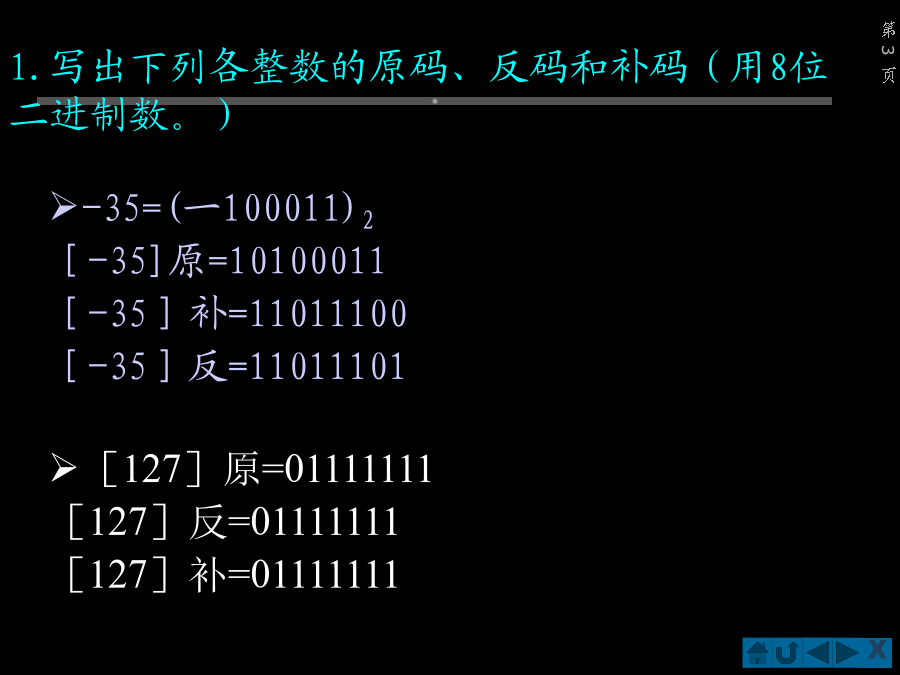

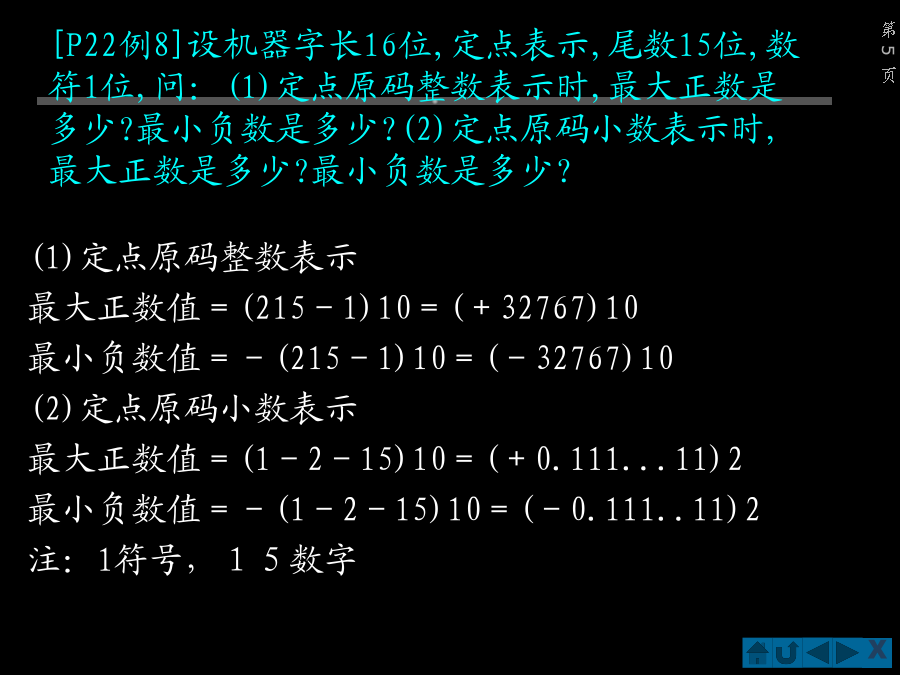

第二章运算方法与运算器一.数据与文字的表示数据格式,数的机器码表示及表数范围二.定点加法、减法运算补码加、减法运算方法溢出的概念和检测方法三.定点乘法运算原码阵列乘法器和补码阵列乘法器的求乘积过程。四.浮点运算浮点数的加、减、乘运算过程。1.写出下列各整数的原码、反码和补码(用8位二进制数。)-127=(-1111111)2[-127]原=11111111[-127]补=10000001[-127]反=10000000[P22例8]设机器字长16位,定点表示,尾数15位,数符1位,问:(1)定点原码整数表示时,最大正数是多少?最小负数是多少?(2)定点原码小数表示时,最大正数是多少?最小负数是多少?[例].在IEEE754标准中,一个规格化的32位浮点数x的真值表示为:(1)27/64=0.011011=1.1011*2-2E=-2+127=125=01111101S=0M=1011000000000000000000010111110110110000000000000000000【例】用变形补码计算x+y,同时指出结果是否溢出。(3)X=-10110y=-00001求x+y[x]补1101010+[y]补1111111_________________[x+y]补1101001【例】已知x和y,用变形补码计算x-y(3)X=11011y=-10011求x-y[x]补0011011+[-y]补0010011_________________[x-y]补0101110【例】.用原码阵列乘法器,补码阵乘法器计算x*y.解:X=11011y=-11111[x]补=011011[y]补=100001乘积符号位单独运算:xf⊕yf=1算前求补输出后:|x|=11011|y|=11111解:X=-11111y=-11011[x]原=111111[y]原=111011乘积符号位单独运算:xf⊕yf=0算前求补输出后:|x|=11111|y|=11011解:X=-11111y=-11011[x]补=100001[y]补=100101乘积符号位单独运算:xf⊕yf=0算前求补输出后:|x|=11111|y|=11011【例】x=0.1101*201y=-0.1010*211尾数和阶符都采用补码表示,都采用双符号位表示法。求x+y[x]浮=0001,00.1101[y]浮=0011,11.0110阶差=1110即为-2Mx应当右移2位,[x]浮=0011,00.0011(01)尾数和为11.1001(01)左规11.0010(10),阶码减1为0010舍入(就近舍入)11.0011丢弃10x+y=-0.1101*210【例】设有浮点数x=2-5×0.0110011,y=23×(-0.1110010),阶码用4位补码表示,尾数(含符号位)用8位原码表示。求[x×y]浮。要求用原码完成尾数乘法运算,运算结果尾数保留高8位(含符号位),并用尾数低位字长值处理舍入操作。P57例30[解:]阶码采用双符号位,尾数原码采用单符号位,则有[Mx]原=0.0110011,[My]原=1.1110010,[Ex]补=11011,[Ey]补=00011[x]浮=11011,0.0110011,[y]浮=00011,1.1110010(1)判断操作是否为”0”,求阶码和[Ex+Ey]补=[Ex]补+[Ey]补=11011+00011=11110,值为补码形式-2。(2)尾数乘法运算可采用原码阵列乘法器实现,即有[Mx]原×[My]原=[0.0110011]原×[1.1110010]原=[1.0101101,0110110]原(3)规格化处理乘积的尾数不是规格化的数,需要左规,阶码变为11101(-3),尾数变为1.1011010,1101100。(4)舍入处理尾数为负数,取尾数高位字长,按舍入规则,舍去低位字长,故尾数为1.1011011。最终相乘结果为[x×y]浮=11101,1.1011011其真值为:x×y=2-3×(-0.1011011)第三章内存储器[例]CPU的地址总线为16根(A15~A0,A0为低位),双向数据总线为8根(D7~D0),控制总线中与主存有关的信号有(允许访存,低电平有效)、(高电平为读命令,低电平为写命令)。使用4K×4位的SRAM芯片,设计一个存储容量为16K×8位的主存储器,画出主存储器与CPU的连接图。某机器中,已知配有一个地址空间为0000H---3FFFH的ROM区域,现再用一个RAM芯片(8K*8)形成一个40K*16位的ROM区域,起始地址为6000H。假设RAM芯片有CS#和WE#信号控制端,CPU地址总线为A15—A0,数据总线为D15—D0,控制信号为R/W#(读/写),MREQ#(访存),要求:(1)画出地址译码

yy****24

实名认证

实名认证

内容提供者

内容提供者

最近下载

一种胃肠道超声检查助显剂及其制备方法.pdf

201651206021+莫武林+浅析在互联网时代下酒店的营销策略——以湛江民大喜来登酒店为例.doc

201651206021+莫武林+浅析在互联网时代下酒店的营销策略——以湛江民大喜来登酒店为例.doc

用于空间热电转换的耐高温涡轮发电机转子及其装配方法.pdf

用于空间热电转换的耐高温涡轮发电机转子及其装配方法.pdf

用于空间热电转换的耐高温涡轮发电机转子及其装配方法.pdf

用于空间热电转换的耐高温涡轮发电机转子及其装配方法.pdf

用于空间热电转换的耐高温涡轮发电机转子及其装配方法.pdf

用于空间热电转换的耐高温涡轮发电机转子及其装配方法.pdf

论《离骚》诠释史中的“香草”意蕴.docx