如果您无法下载资料,请参考说明:

1、部分资料下载需要金币,请确保您的账户上有足够的金币

2、已购买过的文档,再次下载不重复扣费

3、资料包下载后请先用软件解压,在使用对应软件打开

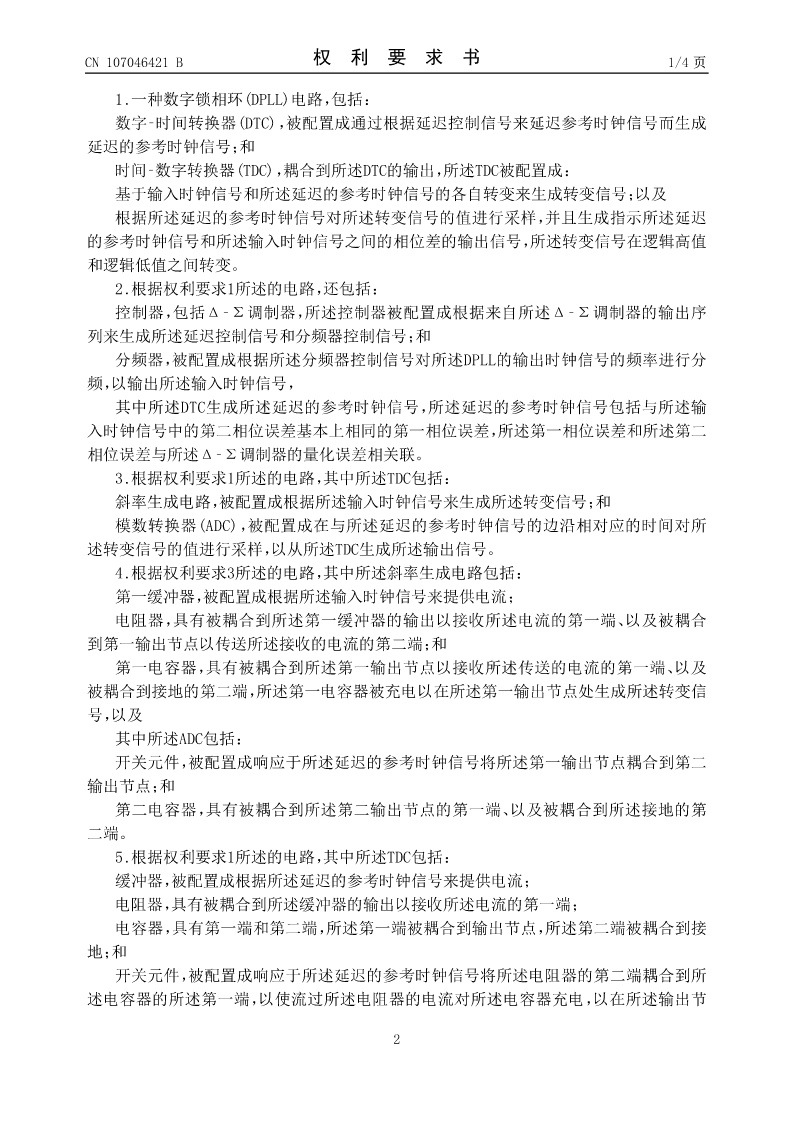

(19)中华人民共和国国家知识产权局 (12)发明专利 (10)授权公告号CN107046421B (45)授权公告日2021.12.21 (21)申请号201710018793.3(51)Int.Cl. (22)申请日2017.01.10H03L7/099(2006.01) (65)同一申请的已公布的文献号(56)对比文件 申请公布号CN107046421AUS2013093471A1,2013.04.18 CN102111149A,2011.06.29 (43)申请公布日2017.08.15CN101160722A,2008.04.09 (30)优先权数据CN103066964A,2013.04.24 62/279,9222016.01.18USUS2005162204A1,2005.07.28 (73)专利权人马维尔亚洲私人有限公司CN104506190A,2015.04.08 地址新加坡新加坡城高源培.应用于全数字锁相环的时间数字转 换器的研究与设计《.中国优秀硕士学位论文全 (72)发明人O·布尔格王海松高翔文数据库信息科技辑》.2016,第I136-59页. (74)专利代理机构北京市金杜律师事务所审查员吴一帆 11256 代理人张维潘聪 权利要求书4页说明书12页附图6页 (54)发明名称 全数字锁相环及其控制方法 (57)摘要 一种数字锁相环(DPLL)电路,包括数字‑时 间转换器(DTC),其被配置成根据延迟控制信号 来延迟参考时钟信号而生成延迟的参考时钟信 号;以及耦合到DTC的输出的时间‑数字转换器 (TDC)。TDC被配置成根据延迟的参考时钟信号对 转变信号的值进行采样,并且生成指示延迟的时 钟信号与输入时钟信号之间的相位差的输出信 号。一种控制DPLL的方法,包括:根据延迟控制信 号来延迟参考时钟信号,根据延迟的参考时钟信 号对转变信号的值进行采样,生成指示延迟的时 钟信号与输入时钟信号之间的相位差的输出信 号,以及根据输出信号来生成数字控制振荡器 (DCO)时钟信号。 CN107046421B CN107046421B权利要求书1/4页 1.一种数字锁相环(DPLL)电路,包括: 数字‑时间转换器(DTC),被配置成通过根据延迟控制信号来延迟参考时钟信号而生成 延迟的参考时钟信号;和 时间‑数字转换器(TDC),耦合到所述DTC的输出,所述TDC被配置成: 基于输入时钟信号和所述延迟的参考时钟信号的各自转变来生成转变信号;以及 根据所述延迟的参考时钟信号对所述转变信号的值进行采样,并且生成指示所述延迟 的参考时钟信号和所述输入时钟信号之间的相位差的输出信号,所述转变信号在逻辑高值 和逻辑低值之间转变。 2.根据权利要求1所述的电路,还包括: 控制器,包括Δ‑Σ调制器,所述控制器被配置成根据来自所述Δ‑Σ调制器的输出序 列来生成所述延迟控制信号和分频器控制信号;和 分频器,被配置成根据所述分频器控制信号对所述DPLL的输出时钟信号的频率进行分 频,以输出所述输入时钟信号, 其中所述DTC生成所述延迟的参考时钟信号,所述延迟的参考时钟信号包括与所述输 入时钟信号中的第二相位误差基本上相同的第一相位误差,所述第一相位误差和所述第二 相位误差与所述Δ‑Σ调制器的量化误差相关联。 3.根据权利要求1所述的电路,其中所述TDC包括: 斜率生成电路,被配置成根据所述输入时钟信号来生成所述转变信号;和 模数转换器(ADC),被配置成在与所述延迟的参考时钟信号的边沿相对应的时间对所 述转变信号的值进行采样,以从所述TDC生成所述输出信号。 4.根据权利要求3所述的电路,其中所述斜率生成电路包括: 第一缓冲器,被配置成根据所述输入时钟信号来提供电流; 电阻器,具有被耦合到所述第一缓冲器的输出以接收所述电流的第一端、以及被耦合 到第一输出节点以传送所述接收的电流的第二端;和 第一电容器,具有被耦合到所述第一输出节点以接收所述传送的电流的第一端、以及 被耦合到接地的第二端,所述第一电容器被充电以在所述第一输出节点处生成所述转变信 号,以及 其中所述ADC包括: 开关元件,被配置成响应于所述延迟的参考时钟信号将所述第一输出节点耦合到第二 输出节点;和 第二电容器,具有被耦合到所述第二输出节点的第一端、以及被耦合到所述接地的第 二端。 5.根据权利要求1所述的电路,其中所述TDC包括: 缓冲器,被配置成根据所述延迟的参考时钟信号来提供电流; 电阻器,具有被耦合到所述缓冲器的输出以接收所述电流的第一端; 电容器,具有第一端和第二端,所述第一端被耦合到输出节点,所述第二端被耦合到接 地;和 开关元件,被配置成响应于所述延迟的参考时钟信号将所述电阻器的第二端耦合到所 述电容器的所述第一端,以使流过所述电阻器的电流对所述电

Ta的资源

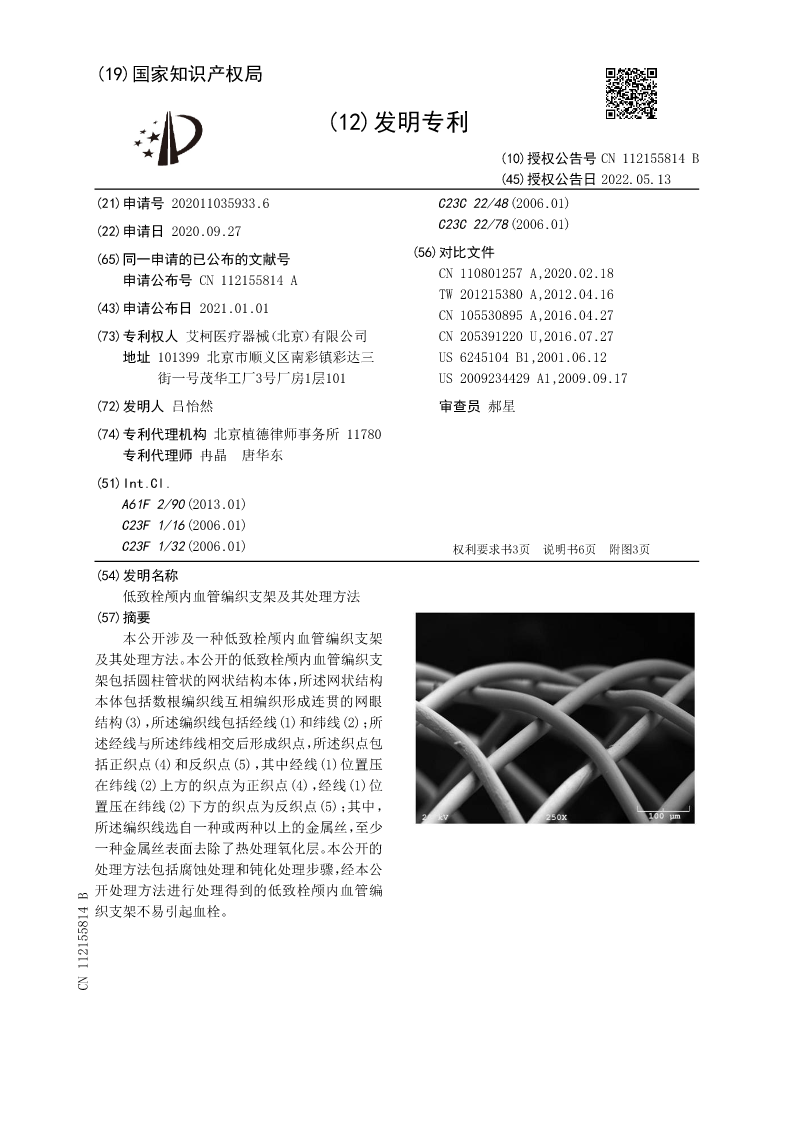

2020110359336低致栓颅内血管编织支架及其处理方法

2020110303186一种钙钛矿量子点聚合物粒子的制备方法

2020110124078基于精准医疗的大数据分析系统及方法

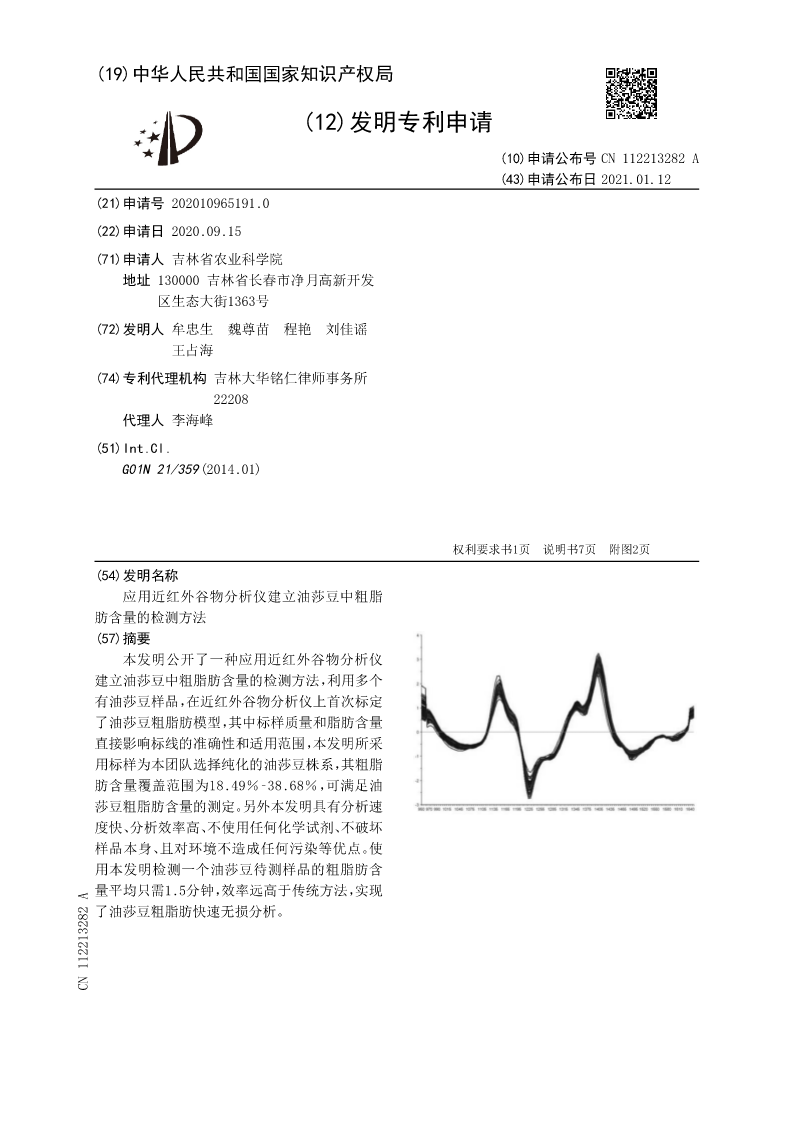

2020109651910 应用近红外谷物分析仪建立油莎豆中粗脂肪含量的检测方法

2020109529321一种铝合金用无氟无氯环保粒状精炼剂及其制备和应用

2020108899336一种新能源商用车总装车间线路布局

2020108620703城市燃气管网多输差协同计算模型及应用方法

2020108207369一种微交联阳离子型聚丙烯酰胺絮凝剂及其制备方法与应用

2020108035131一种基于全站仪的激光雷达外部参数标定方法

2020107682859一种内燃机等离子节油器阴阳极的制备方法

13****40

实名认证

实名认证

内容提供者

内容提供者

最近下载